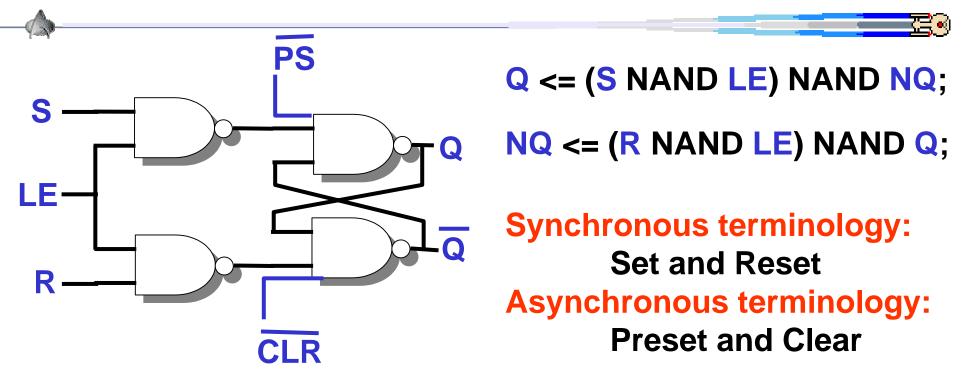

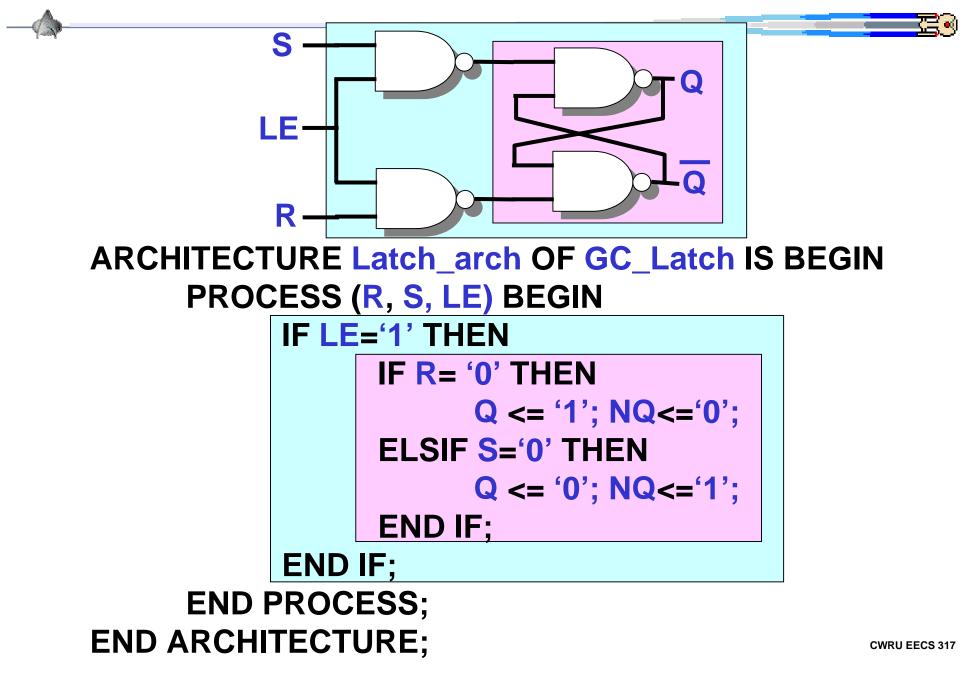

### Gated-Clock SR Flip-Flop (Latch Enable)

Latches require that during the gated-clock the data must also be stable (i.e. S and R) at the same time

Suppose each gate was 5ns: how long does the clock have to be enabled to latch the data?

Answer: 15ns

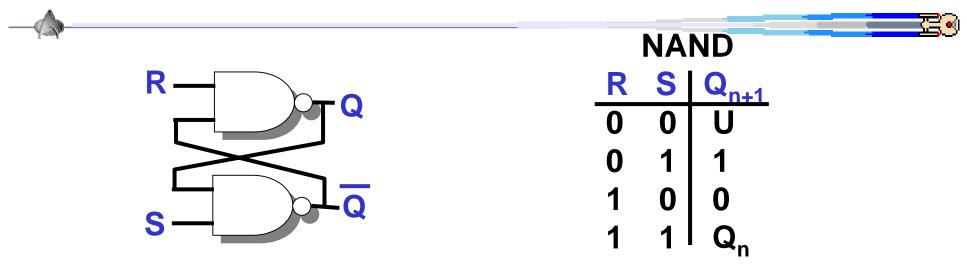

### **Structural SR Flip-Flop (Latch)**

ENTITY Latch IS PORT(R, S: IN std\_logic; Q, NQ: OUT std\_logic); END ENTITY;

ARCHITECTURE latch\_arch OF Latch IS BEGIN

Q <= R NAND NQ; NQ <= S NAND Q; END ARCHITECTURE;

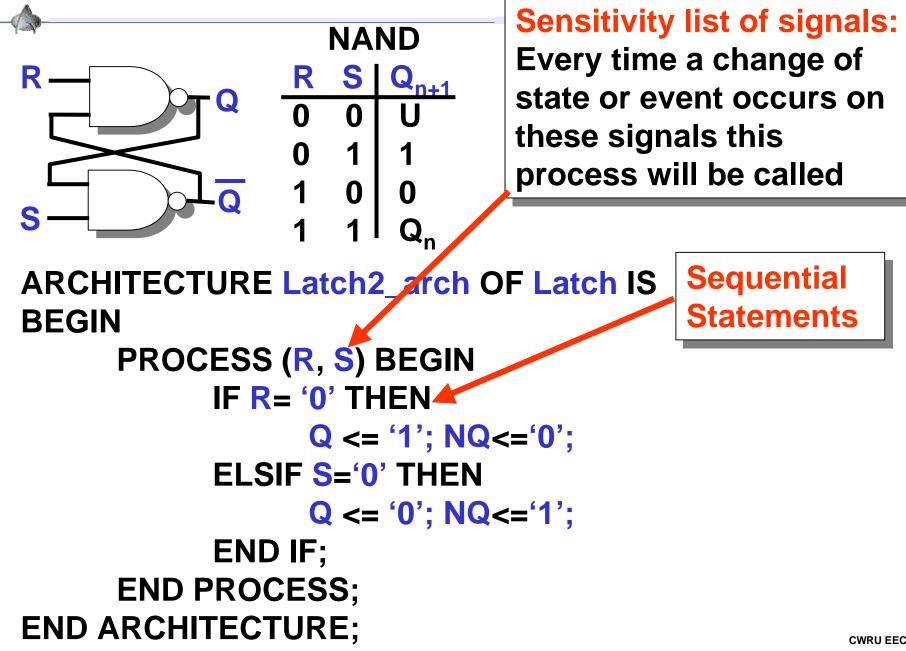

## Inferring Behavioral Latches: Asynchronous

### Gated-Clock SR Flip-Flop (Latch Enable)

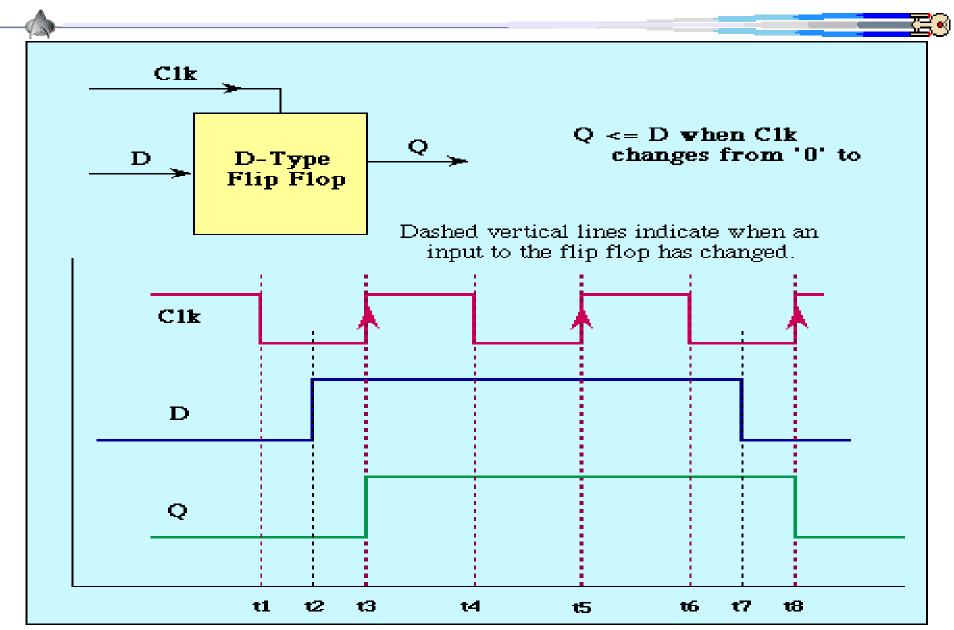

### **Rising-Edge Flip-flop**

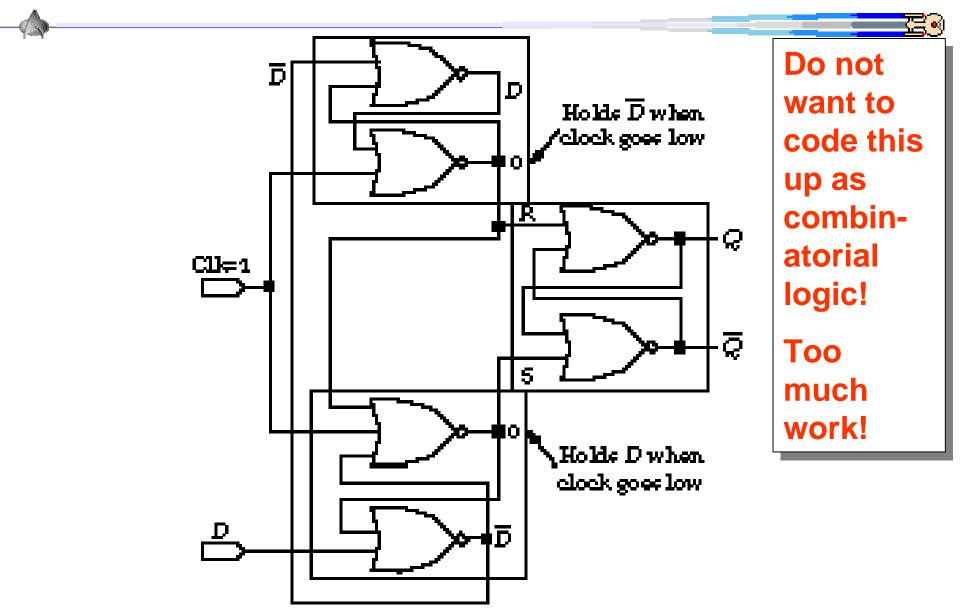

### **Rising-Edge Flip-flop logic diagram**

Figure 6.24 Negative edge-triggered D flip-flop when clock is

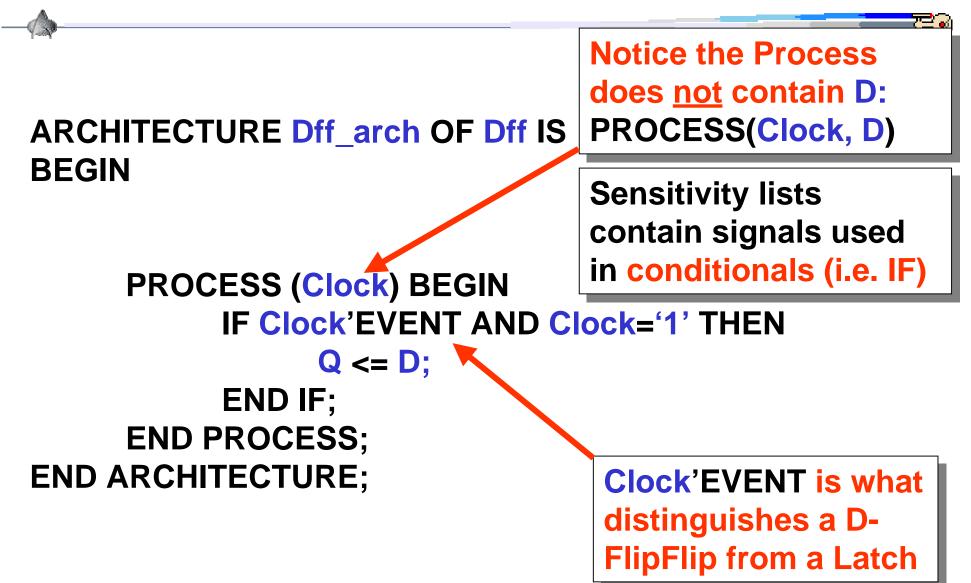

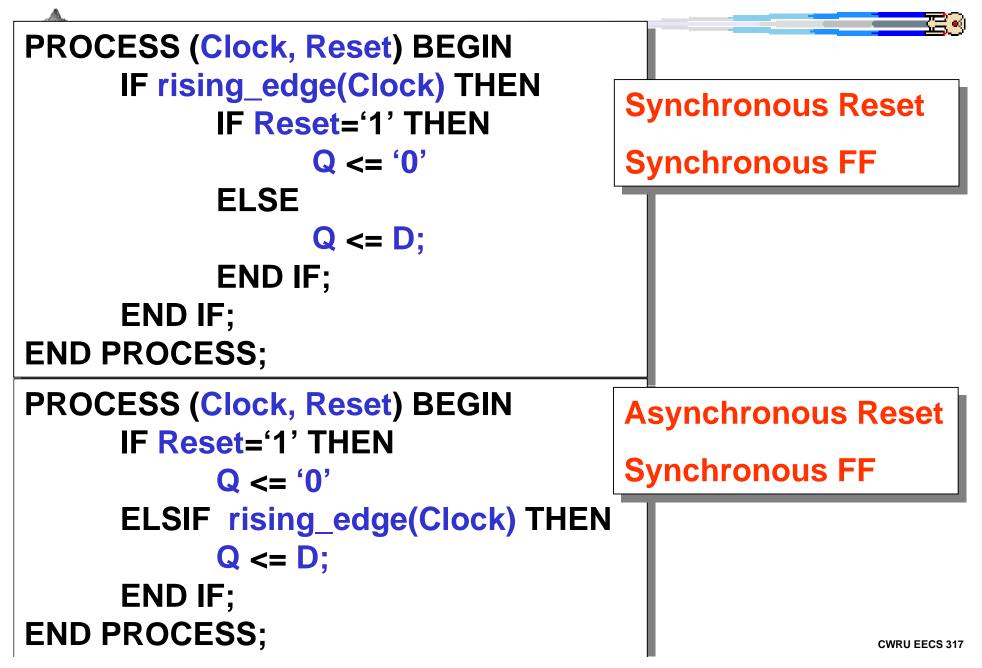

## **Inferring D-Flip Flops: Synchronous**

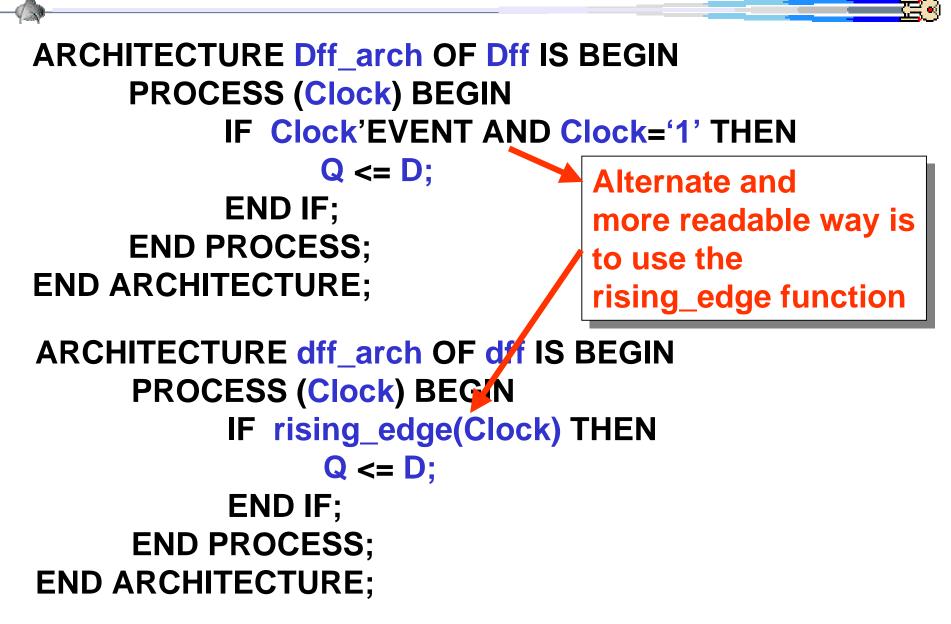

### Inferring D-Flip Flops: rising\_edge

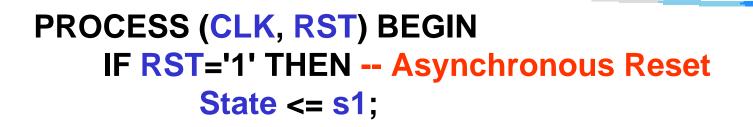

## **Inferring D-Flip Flops: Asynchronous Reset**

ARCHITECTURE dff\_reset\_arch OF dff\_reset IS BEGIN

```

PROCESS (Clock, Reset) BEGIN

```

IF Reset= '1' THEN -- Asynchronous Reset Q <= '0' ELSIF rising\_edge(Clock) THEN --Synchronous Q <= D; END IF; END PROCESS;

END ARCHITECTURE;

## **Inferring D-Flip Flops: Synchronous Reset**

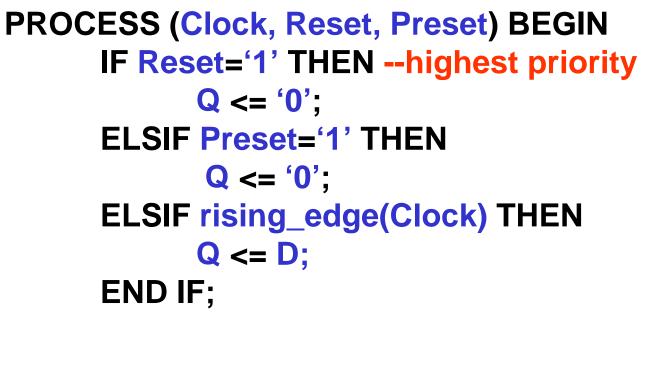

### **D-Flip Flops: Asynchronous Reset & Preset**

**END PROCESS;**

## **VHDL clock behavioral component**

```

ENTITY clock_driver IS

```

```

GENERIC (Speed: TIME := 5 ns);

```

```

PORT (Clk: OUT std_logic);

```

END;

ARCHITECTURE clock\_driver\_arch OF clock\_driver IS

SIGNAL Clock: std\_logic := '0';

BEGIN

```

Clk <= Clk XOR '1' after Speed;

```

```

Clock <= Clk;

```

END ARCHITECTURE;

CONFIGURATION clock\_driver\_cfg OF clock\_driver IS FOR clock\_driver\_arch END FOR; END CONFIGURATION;

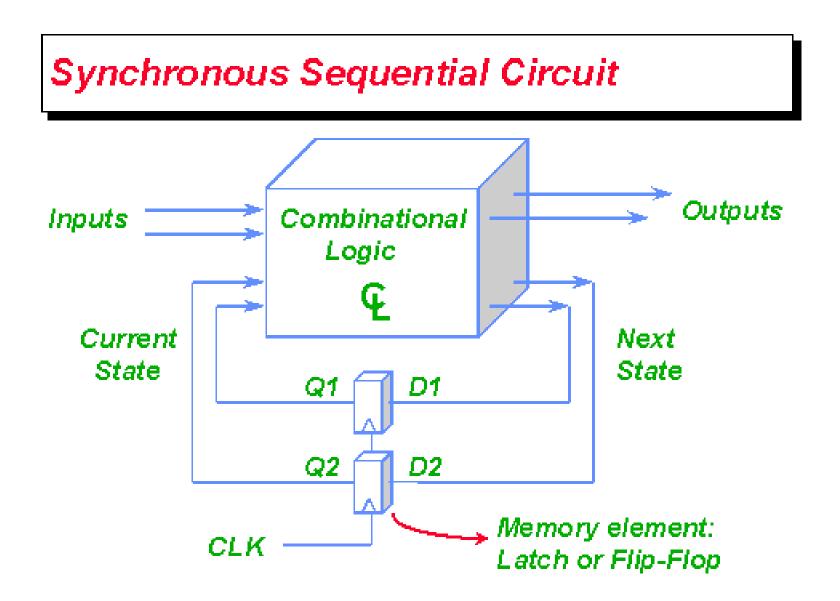

#### Issues: Specification, design, clocking and timing

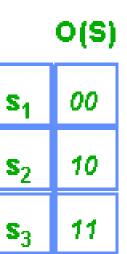

### Abstraction: Finite State Machine

- A Finite State Machine (FSM) has:

- K states, S = {s<sub>1</sub>, s<sub>2</sub>, ..., s<sub>K</sub>}, initial state s<sub>1</sub>

- N inputs, I =  $\{i_1, i_2, ..., i_N\}$

- M outputs,  $O = \{o_1, o_2, ..., o_M\}$

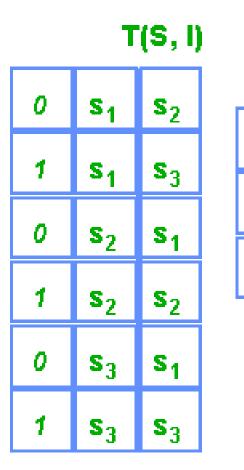

- Transition function T(S, I) mapping each current state and input to a next state

- Output function O(S) mapping each current state to an output

- Given a sequence of inputs the FSM produces a sequence of outputs which is dependent on s<sub>1</sub>, T(S, I) and O(S)

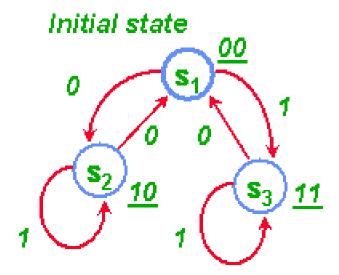

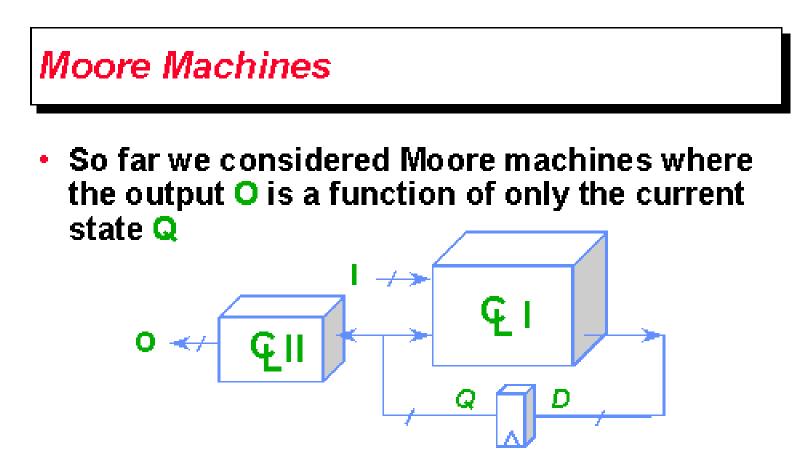

### FSM Representations

State Transition Graph

|          | t  | t+1 | <i>t</i> +2 |

|----------|----|-----|-------------|

| Inputs:  | 0  | 1   | 0           |

| Outputs: | 00 |     |             |

State Transition Table

Moore FSM State Transition Graph

--State Encoding is sequentially done by VHDL

TYPE FSMStates IS (s1, s2); --s1=0, s2=1

SIGNAL State, NextState: FSMStates;

$$o_1 = 0$$

$i_1 = 1$

$i_1 = 1$

$i_1 = 1$

$i_1 = 1$

$i_1 = 0$

$i_1 = 0$

$i_1 = 1$

$i_1 = 0$

State Encoding: Choose a <u>unique</u> binary code for each s<sub>i</sub> so the combinational logic can be specified

- Choose  $s_1 = 1$  and  $s_2 = 0$

– The non-sequential case requires the following

ATTRIBUTE FSMencode: string;

ATTRIBUTE FSMencode of FSMStates: TYPE IS "1 0";

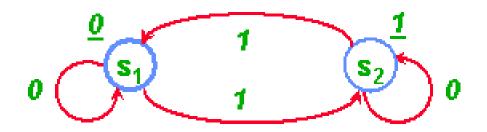

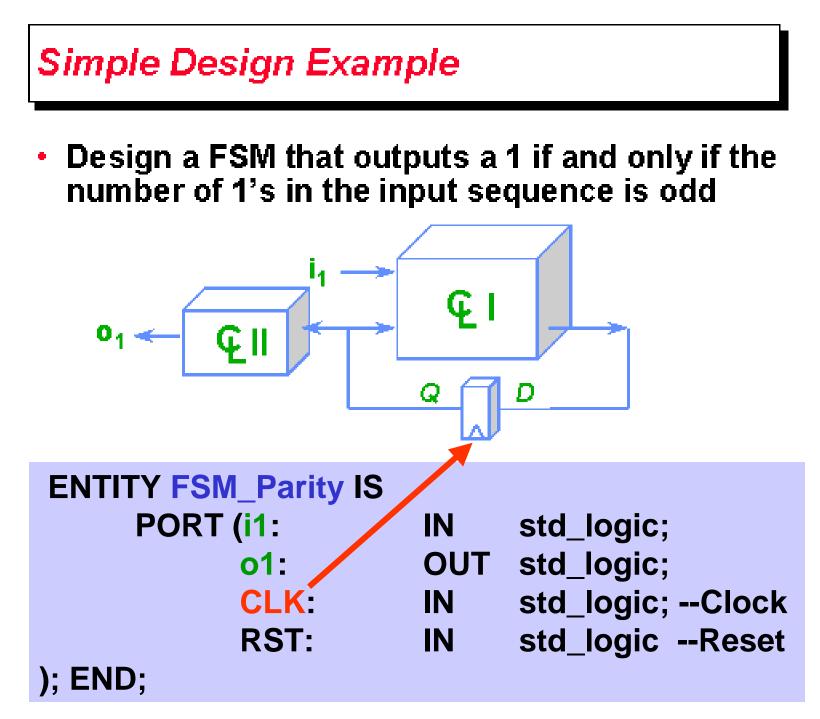

### Simple Design Example

$$i_1 = 0$$

$(s_1 = 1)$   $i_1 = 1$   $(s_2 = 1)$   $i_1 = 0$   $i_1 = 0$

## FSM Controller: Current State Process

```

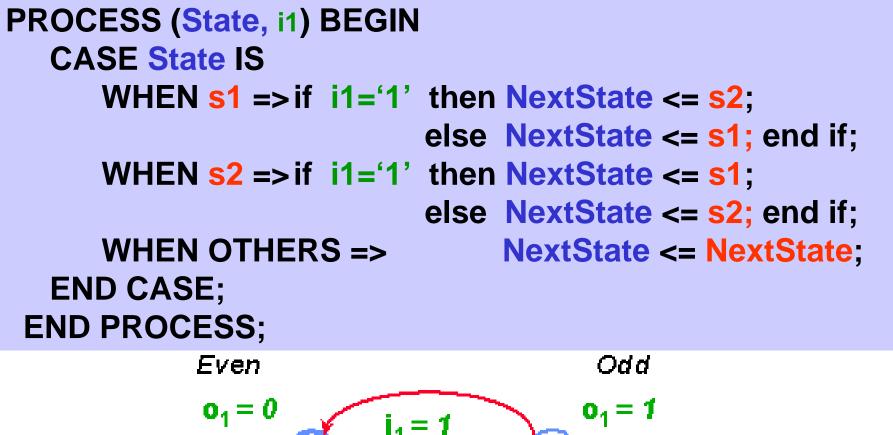

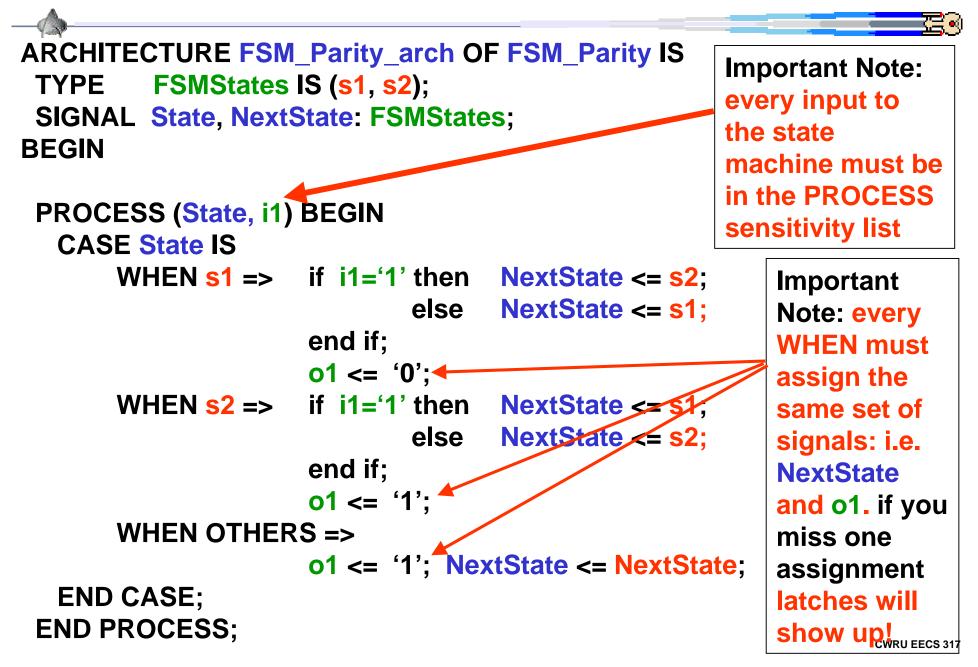

ARCHITECTURE FSM_Parity_arch OF FSM_Parity IS

TYPE FSMStates IS (s1, s2);

SIGNAL State, NextState: FSMStates;

BEGIN

```

```

PROCESS (State, i1) BEGIN

CASE State IS

WHEN s1 => if i1='1' then NextState <= s2;

else NextState <= s1; end if;

WHEN s2 => if i1='1' then NextState <= s1;

else NextState <= s2; end if;

WHEN OTHERS => NextState <= NextState;

END CASE;

END PROCESS;

WITH State SELECT

01 <= 0' WHEN s1,

'1' WHEN s2,

'1' WHEN OTHERS; --X, L, W, H, U

```

## **Alternative: less coding**

### FSM controller: NextState Process

ELSIF rising\_edge(CLK) THEN State <= NextState; END IF; END PROCESS;

**END ARCHITECTURE;**

CONFIGURATION FSM\_Parity\_cfg OF FSM\_Parity IS FOR FSM\_Parity\_arch END FOR; END CONFIGURATION;

# Logic Implementations Synthesis

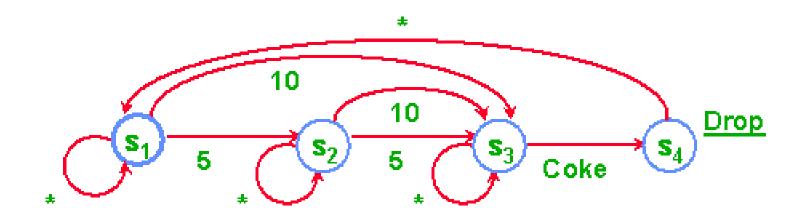

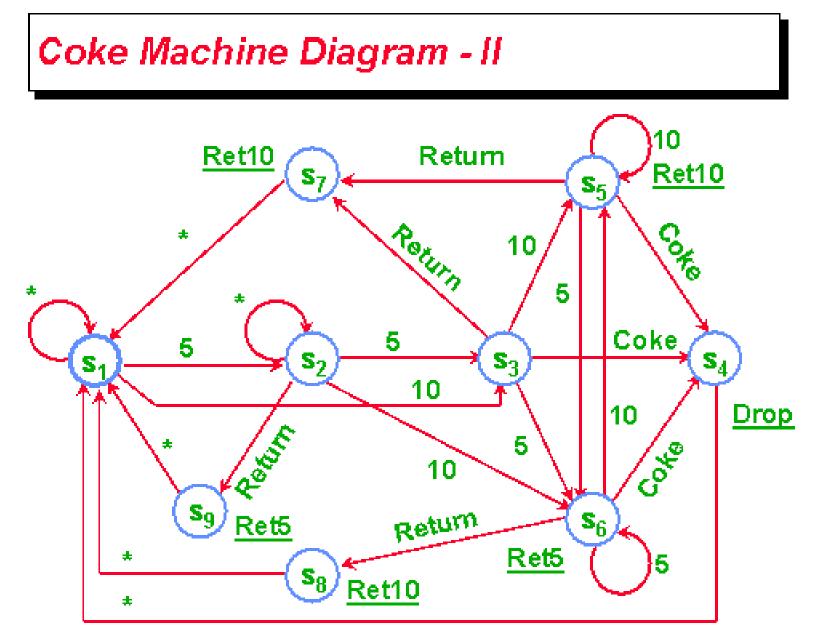

### **Coke Machine Example**

- Coke costs \$.10

- Only nickels and dimes accepted

- FSM inputs:

- 5: Nickel

- 10: Dime

- Coke: Give me a coke

- Return: Give me my money back

- FSM outputs:

- Drop: Drop a coke

- Ret5: Return \$.05

- Ret10: Return \$.10

| COKE |  |  |  |

|------|--|--|--|

|      |  |  |  |

|      |  |  |  |

### Coke Machine State Diagram

#### Assumption: At most one input among Coke, 5, 10, and Return is asserted

\* represents all unspecified transitions from state

Does this work?

After Return input, any input in the next cycle is ignored!

11

# Assignment #6

a) Write the VHDL synchronous code (no latches!) and test bench for the coke II machine. Note: the dc\_shell synthesis analyze command will tell you if you inferred latches. Hand code and simulation using the Unix script command.

b) Synthesize the your design and hand in the logic diagram, Unix script include cell, area, timing report.