for various energy levels of protection with minimal power consumption and write time penalties.

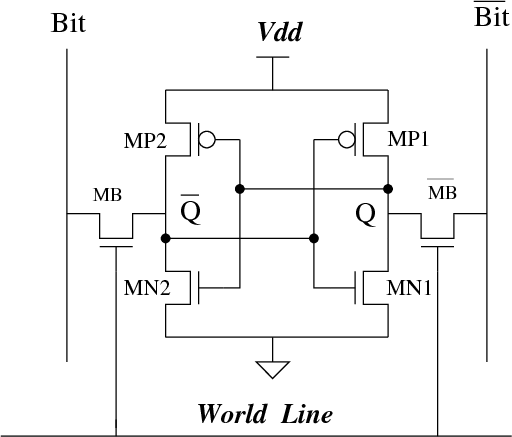

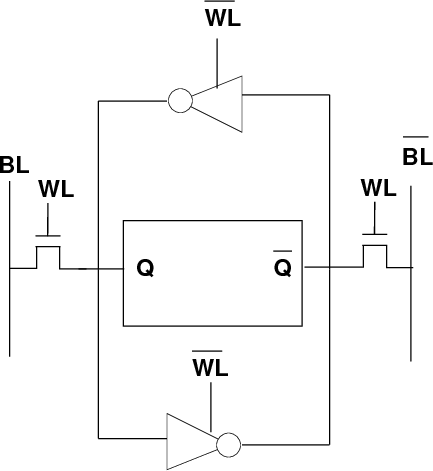

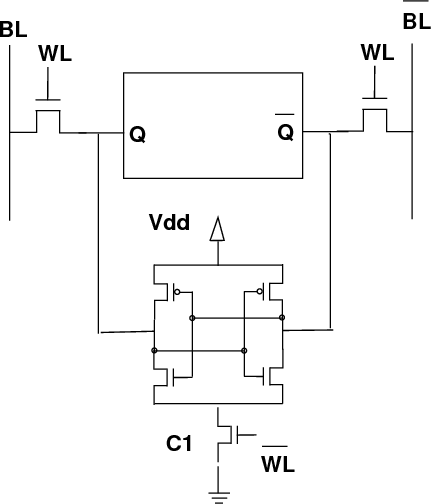

Our model is based on a classic 6 transistor inner core SRAM cell and an outer core consisting

of enhanced tri-state inverters. The outer core will absorb a particle strike at a sensitive node

of the SRAM cell without a major impact on write time performance or area overhead.

The model provides an on-demand protection due to the fact that the outer core

can be shut off during non-essential operating mode. The on-demand aspect of the design provides a

much more favorable power consumption overhead compared to the existing hardening technique.

The gains in power consumption overhead reduction increase as we scale down the process technology from 90nm

to 32nm. We simulated extensively our model and provided results for various energy levels of

soft error protection. We also compared our method to the standard hardening technique in terms of layout area,

performance and power consumption overhead for for 90nm, 65nm, 45nm and 32nm process technologies.

Regular Memory Cell SRAM with Tri-State Inverters SRAM Protected

Simulation Results

We demonstrated how the design of our SRAMT cell provides advantages in terms of performance and power consumption overhead

compared to the existing soft error protection techniques through transistor hardening.

Through simulations we were able to demonstrate that our new design provides identical energy levels of protection

to the existing protection techniques at minimal area overhead, while providing advantages in write time delay performance

and great reduction in power consumption for both average power and peak power during write time operation.

Our solution is also technology scalable, which is especially crucial for submicron designs.

References

Aravind Rajendran, Yuriy Shiyanovskii, Frank Wolff, Chris Papachristou. Noise Margin, Critical Charge and Power-Delay Tradeoffs for SRAM Design,

IEEE Internat. Symp. on On Line Testing (IOLTS-2011), July 2011. IOLTS-2011

Yuriy Shiyanovskii, Aravind Rajendran, Chris Papachristou. A Novel Radiation Tolerant SRAM Design Based on Synergetic Functional Component Separation for Nanoscale CMOS,

IEEE Internat. Symp. on On Line Testing (IOLTS-2011), July 2011. IOLTS-2011

Yuriy Shiyanovskii, Frank Wolff, Chris Papachristou. SRAM Cell Design Using Tri-state Devices for SEU Protection,

IEEE Internat. Symp. on On Line Testing (IOLTS-2009), July 2009. IOLTS-2009

Yuriy Shiyanovskii, Frank Wolff, Chris Papachristou. SRAM cell design protected from SEU upsets,

IEEE Internat. Symp. on On Line Testing (IOLTS-2008), July 2008. IOLTS-2008

Balkaran Gill, Chris Papachristou, Frank Wolff. A New Asymmetric SRAM Cell to Reduce Soft Errors and Leakage Power in FPGA,

IEEE Internat. Conf. on Design Automation in Europe (DATE-2007), DATE-2007

Balkaran Gill, Chris Papachristou, Frank Wolff. Soft Delay Error Analysis in Logic Circuits,

IEEE Internat. Conf. on Design Automation in Europe (DATE-2006), March 2006. DATE-2006

Balkaran Gill, Chris Papachristou, Frank Wolff, Norbert Seifert. Node Sensitivity Analysis for Soft Errors in CMOS Logic,

IEEE Internat. Test Conf. (ITC-2005), November 2005, ITC-2005