| Week | Lectures | Required Readings | Assignments |

| Week #1: 01.11T, 01.13TH | Logic Gate Notation: |

1 |

2 | Timing Diagrams: | 1 | 2 | 3 | 4 |

|

Wakerly: Logic Gates: p1-14, 79-84, 193-198, Logic Bubbles: Section 4.3.2, p217-219, Bubble-to-Bubble Design: Section 5.1.5, p320, Fig. 5-6, Fig. 5-7, Fig. 5-8, Fig. 5-11. Exclusive-OR, XOR: Section 5.8, p410-413. |

Due Tuesday, 1.18: Homework #1 Solutions for Homework #1 |

| Week #2: 01.18T, 01.20TH | Logic Gate Delay: |

1 |

2 | DeMorgan, Feedback, Tri-State: 1 | 2 | 3 | 4 |

|

DeMorgan: Fig. 4-3, 4-4, p201-2, Fig 5-4, p317

Delay Timing: Fig 3-36, p114, Section 3.6.2, p119; |

Due Tuesday, 1.25: Homework #2 Solutions for Homework #2 |

| Week #3: 01.25T, 01.27TH | Delay Timing, CMOS, AOI: |

1 |

2 |

3 |

|

Wakerly CMOS: sections 3.1-3.3.7, pages 79-95. Resistors, LEDs: Sections 3.7.5-3.7.8, pages 129-135. |

Download: | Windows Spice |

MacSpice | Due Tuesday Feb 1: Homework #3

|

| Week #4: 02.01T, 02.03TH | SPICE PWL, AOI: |

1 |

2 |

3 | Exam #1 on Thurs Feb 3: | Soln #1 |

|

Wakerly | |

| Week #5: 02.08T, 02.10TH | Diodes, LEDs, Resistors: |

1 |

2 |

NMOS 2n7000 | Binary, Precision, Endian: | 1 | 2 |

|

Wakerly chapter 2 LED | Inside an LED | Medical uses | Diode OR-gate | Resistor | Capacitor |

|

|

| Week #6: 02.15T, 02.17TH |

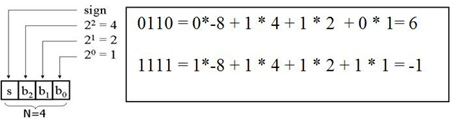

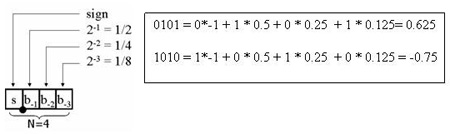

One's & Two's Complement, AND, OR, XOR: |

1 |

2 |

3 |

4 |

|

Download the following: Install jre: | Look for "Java Software Download" | Download: | hello51.asm | hello51.lst | hello51.hex | Intel file.hex format | Download Simulator: | j51.jar | j51.conf | j51 website | Download Assembler: | as31 manpage | as31 for Windows PC | as31 for Solaris | as31 website for all others | 8051 Docs: | Summary | tutorials | instructions | opcodes | as31 assembler | Intel file.hex format | architecture | hardware | boolean |

|

Due Tuesday Feb 22: |

Lab #1 |

HW #4 |

HW#4 soln. |

Email #2 |

Email #1 |

Old HW Soln. |

|

| Week #7: 02.22T, 02.24TH | 8051 strings, atoi: |

1 |

2 |

3 | 8051 shifts, precedence: | 1 | 2 | 3 |

|

Links: |

Intel file.hex format |

base64 |

base64 example |

Paris Hilton's Address Book |

Cobol Comp-3 BCD |

Father of ASCII |

|

Due Tuesday March 1: | HW #5 | Email #1 |

|

| Week #8: 03.01T, 03.03TH |

Exam Review: |

1 |

2 |

3 |

4 |

Exam #2: |

Precedence: | C++ Chart |

mime: | base64 |

base64 example | Reading: Wakerly Chapter 2 Solutions: | HW#4 soln. |

|

|

| Week #9: 03.08T, 03.10TH | Spring Break | ||

| Week #10: 03.15T, 03.17TH | 8051 loops: |

1 |

2 |

3 | 8051 simulator, compare ops: | 1 | 2 | 3 | sim8051.cpp | hexfin.txt |

|

Solutions to Exam #2 soln Wakerley Chapter 4-4.5.4: Algebra, SOP, k-maps, Quine-McCluskey, Hazards |

Due March 3 Thursday HW #6 Replace 1 exam with Project

|

| Week #11: 03.22T, 03.24TH | 8051 calls, k-map: |

1 |

2 |

3 |

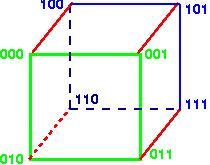

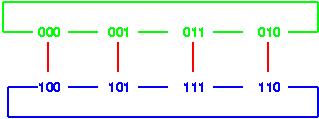

4 | k-cube, k-map, SOP: | 1 | 2 | 3 |

|

Project info: | Wakerly page 520, section 6.3.7 Tic-tac-Toe | Strategy | Magic Square | Functions | Possible Wins | EDSAC Simulator | EDSAC Tic-Tac-Toe | | Download (for Lab #2): espresso |

| Week #12: 03.29T, 03.31TH | Quine-McClusky, 4-cube: |

1 |

2 | Multi-output k-map, Static-1 hazard k-map: | 1 | 2 |

|

K-map: |

k-map & QM Lectures |

K-map Intro |

K-map Slides |

K-map freeware |

Boolean Algebra Study Problems 1-4: | MIT | with Solns | PLA 82S100 | PAL 16L8 | PROM 74188 | Logic Gate Growth | Wakerly section 5.3 Multi-Output Minimization Example | Wakerly 4.3.8

|

Due: April 7 Thursday: Homework #7 Extra Credit (must complete each assignment fully): Study Wakerly 5.10.1-5.10.2 and implement the 4-bit adder: EC1: SPICE Extra Credit #1 (20 points, Due: April 21): Implement 4-bit ripple adder using SPICE and subckts: ADD4 calls ADD1 calls XOR calls NAND, NOR. Hand-in commented source code and screen shots of simulator after adding several numbers (1111+0001; 1010+0101; and 0111+0011). EC2: VHDL Extra Credit #2 (30 points, Due: April 21): | EC2 Tutorial | addfull.vhd | addfulltb.vhd | Simulator | |

| Week #13: 04.05T, 04.07TH | Exam #3: Thursday April 7th Exam #3: | Exam #3 soln | Exam #3 | Hw6 & Maxterms, Minterms, Review of Old Exam: | 1 | 2 | 3 | Practice: Old Exam | Old Hw #5 | Old Sample Exam |

|

Exam will cover: Wakerly Chapter 4, pages 193-248, Hw#6, Hw#7, Old Exams, Boolean Algebra, Minterms, SOP, DNF, PLA (pages 337-348) Maxterms, POS, CNF, ROM (pages 832-383) k-map (with/without Don't Cares) Static Hazards, Quine-McCluskey (with/without Don't cares) 8051, and recurrence equations. |

|

| Week #14: 04.12T, 04.14TH |

Add, Sub, Cmp, RTL: |

1 |

2 |

3 |

Latches, State machines: | 1 | 2 | 3 |

|

Wakerly 7, pages 529-560, 573-576.

ALU: Wakerly section 5.10 & 5.11.1

|

Due Tuesday April 19, 2005: homework #8 |

| Week #15: 04.19T, 04.21TH | Exam #4 & Project: Thursday April 21th Moore machines: | 1 | 2 | 3 | Pavlov | Hints: | HW#6 | HW#6 soln. | 2004F | 2004F soln. | Sign(a-b) | |

FSM links: |

#1 | RE/grep links: | #1 | #2 | #3 | #4 |

|

| Week | Lectures | Required Readings | Assignments |

| 1 08.23 |

Digital Modeling: | 1 | |

Megahertz |

Clock speed |

MIPS

|

Due: 09.07T |

| 2 08.31 | Digital Logic Gates: |

1 |

2 |

3 |

4 |

5 |

6 | Truth Tables to CMOS: | 1 | 2 | 3 | 4 | 5 | 6 |

|

Wakerly: Sections 3.1-3.7.5

|

Due: 09.09TH: Wakerly Problems 3.1, 3.10, 3.14, 3.23a, 3.32a, 3.39-40, 3.61-62, 3.65, 3.76, 3.78, 3.80-81 (tips: see Wakerly Website) |

| 3 09.07 | Logic Gate Delay and Area: |

1 |

2 |

3 |

4 |

5 |

6 |

|

Assignment: Homework #1 Solution

|

Practice: Exam #1

|

| 4 09.14 |

Exam #1 solutions Number Systems: | 1 | 2 | 3 | 4 |

|

Wakerly: Sections 2:1-16

|

|

| 5 09.21 |

Negative Numbers and Shifting: |

1 |

2 |

3 | Fractions and precedence: | 1 | 2 | 3 |

|

ECC |

ECC Demo |

|

Due 09.28T: Homework #3 |

| 6 09.28 |

Bit operations di : |

1 |

2 |

3 |

4 | Hamming, n-cube, k-maps: | 1 | 2 | 3 | 4 | 5 |

|

Wakerly: Sections 4.3.3-8 base64 | base64 example |

|

Due 10.07TH: Homework #4

|

| 7

|

SOP = minterms = full cubes = k-map: |

1 |

2 |

3 |

4 |

|

Assignment Solutions Homework #3 Assignment Solutions Homework #4 Practice: Exam #2

|

|

| 8 10.12 |

Exam #2 solutions k-map & Quine-McClusky: | 1 | 2 | 3 |

|

Wakerly: Sections 4.1-4.5.2 (pages 193 to 246)

|

Due 10.21TH: Extra Credit (Exam 1) xor (Exam 2) xor (Exam 3)

|

| 9

|

4-cube k-map: |

1 |

2 |

|

|

K-map Intro |

K-map Slides |

K-map freeware |

|

Due 10.26T: Homework #5

|

| 10 10.26 |

Boolean Algebra, PAL, PAL, & ROM: |

1 |

2 |

3 | HW5, Multiple-Output Minimization & PLA: | 1 | 2 | 3 | 4 |

|

Lecture Slides: k-map & QM Study Problems 1-4: | MIT | with Solns | PLA 82S100 | PAL 16L8 | PROM 74188 | Logic Gate Growth | Wakerly section 5.3 Multi-Output Minimization Example | Wakerly 4.3.8

|

Solutions to Homework #5 Practice Exam #3

|

| 11 11.02 | Exam #3 |

ALU: Wakerly section 5.10 & 5.11.1 Decoders: | PROM 74188 | | ROM | Wakerly section 5.4-5.4.4 Multiplexers: Wakerley section 5.7-5.7.1 Parity: Wakerly section 5.8.1-4 Comparator: Wakerly 5.9.1

|

|

| 12 11.09 |

Multi-precision & Dataflow: |

1 |

2 |

3 | Moore State machines: | 1 | 2 | 3 | 4 |

|

FSM links: |

#1 | RE/grep links: | #1 | #2 | #3 | #4 |

|

Due 11.16T: Homework #6 Due 11.23T: Extra credit #3 (35 points)

|

| 13 11.16 |

Dataflow & Timing diagrams: |

1 |

2 |

3 |

4 | Regular expressions & D-FlipFlop: | 1 | 2 | 3 | 4 |

|

Exam: Sample Exam #4 Wakerly 7, pages 529-560, 573-576. |

Solutions: Homework #6 Solutions: Exam #3

|

| 14 11.23 |

Solutions to Exam #4

|

||

| 15 11.30 |

Exam #5 review: |

Sign(a-b) |

1 |

2 |

3 |

4 | Exam #5 |